Using the Speculative Tomasulos Described in Class

Mem cdb commit 3-4 5 6 - 13 14 - 5-6 1 7 18 Instruction issue robResStat FUEX L. Issue and Completion per Clock Cycle Using Tomasulos Algorithm The Use of a Reorder Buffer Assumptions.

Speculative Taint Tracking Stt A Comprehensive Protection For Speculatively Accessed Data December 2021 Communications Of The Acm

Computer Science questions and answers.

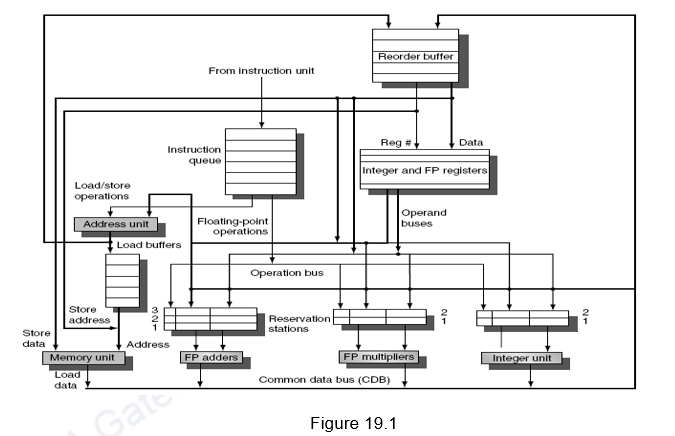

. Instructions issue in-order but execution may be out-of-order as it is done as soon after issue as operands are available. Renames destinations by allocating new physical register Tomasulos scheme. Because of renaming the direct data flow between two instructions cannot be affected by any instructions after them.

Simulation of speculative tomasulo algorithm in C with QT. Artifact of using the same storage location variable name Can be avoided by renaming the conflicting source or destination operands Last class. Problem 1 40 points This problem concerns Tomasulos algorithm.

Please write your name and NetID clearly on the first page. It is the solution to the same kind of problem you had on your homework but for a machine with a slightly different MIPS configuration. ADDD F0 F2 F4 DIVD F6 F6 F0 SUBD F0 F12 F14.

Contribute to Lucas1JorgeSpeculative_Tomasulo_Algorithm development by creating an account on GitHub. View ta02doc from CHE 10 at Jefferson Academy - 64. Big simplification in this lecture.

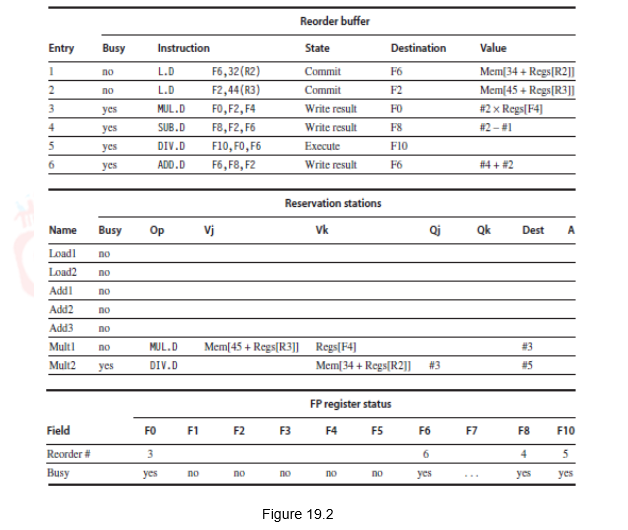

Due IN CLASS on 1052017. Assume we have a MIPS machine that uses the speculative version of Tomasulos algorithm. Assume that we use Speculative Tomasulo Algorithm with Reorder Buffer to run the following code sample.

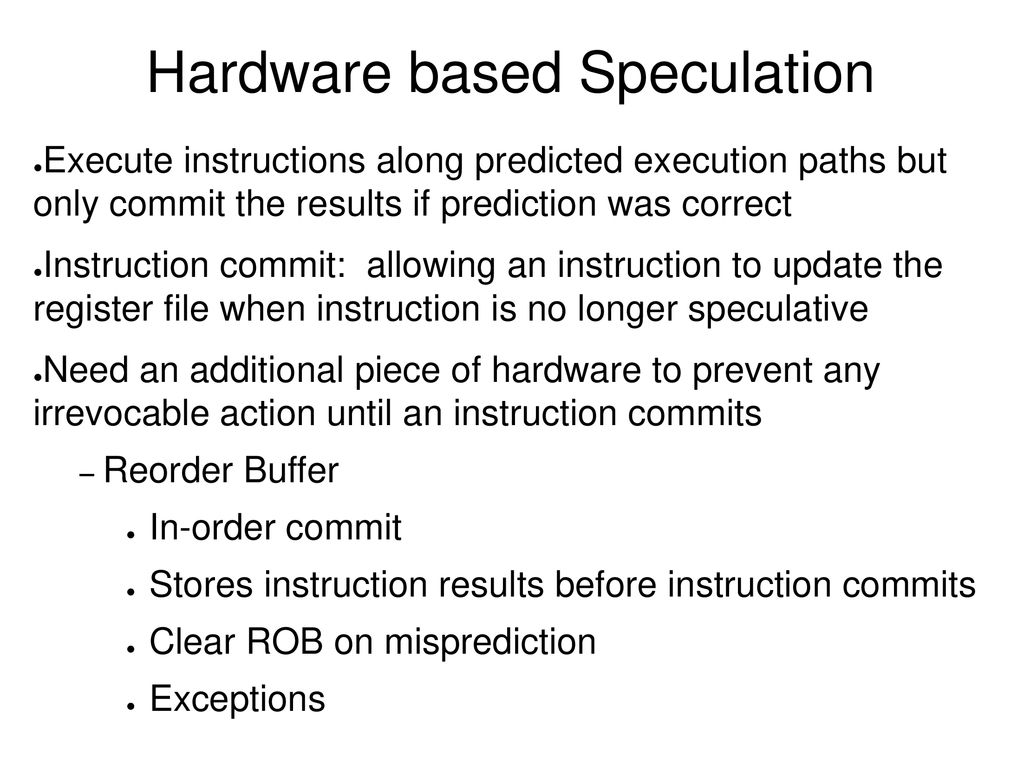

Speculation or speculative execution is the issue and execution of instructions past a. Consider the following speculative Tomasulos algorithm table. Four Steps of Speculative Tomasulo Algorithm.

These in turn implement a renaming and. Renames source operand 1. Assume that we use Speculative Tomasulo Algorithm.

Assume we have a RISC-V machine that uses the speculative version of Tomasulosalgorithm. In hardware speculation eg for Tomasulos algorithm will an. Write result finish execution WB.

Execution operate on operands EX When both operands ready then execute. This project will implement the algorithms for dynamic scheduling and speculative execution using Tomasulos Algorithm. By contrast in the example using Tomasulos algorithm the SUBD and ADDD instructions could both complete before the MULD raised the exception.

- GitHub - dukileeSpeculativeTomasulo. 10 Tomasulo and Speculative Execution Example. Simulation of speculative tomasulo algorithm in C with QT.

View In hardware speculation eg for Tomasulos algorithm will andocx from CS MISC at Bulawayo Polytechnic College. Two main features of Tomasulos Algorithm are the implementation of reservation stations and the common data bus 11. Communications questions and answers.

Due in class on 1052017 Instructions. The result is that the registers F8 and F6 destinations of the SUBD and ADDD instructions could be. Tomasulo and Speculative Execution Tomasulos Property.

Memory scheduling Pretend register algorithm magically knows memory dependences. Register renaming more flexibility better performance We focus on Tomasulos algorithm in the lecture No test questions on scoreboarding Do note that it is used in certain GPUs. Refer to the course fact sheet for policies on collaboration.

LD FO OR1 SUBD F4 F2 FO MULD F2 F4 F6 DADDIU R1 R1 -8 BNE R1 LD F8 R2 ADDD F8 F8 FO DADDIU R2 R2. Issueget instruction from FP Op Queue. Issue get instruction from FP Op Queue If reservation station free no structural hazard the scoreboard issues instr sends operands renames registers.

CDA5155CDA4150 - Spring 2022 Assignment 5 TomasulosAlgorithm ObjectivesLearn howinstruction proceed through an out-of-order OoO processor using a speculative version of Tomasulosalgorithm. For destination this stage sometimes called dispatch Executionoperate on operands EX When both operands ready then execute. If reservation station and reorder buffer slot free issue instr send operands reorder buffer no.

Functional Unit Type Cycles in EX. If not ready watch CDB for result 3. Consider the following architecture specification.

If not ready watch CDB for result. Three Stages of Tomasulo Algorithm 1.

Dynamic Scheduling And Speculation Ppt Download

Dynamic Scheduling With Speculation Computer Architecture

Speculative Taint Tracking Stt A Comprehensive Protection For Speculatively Accessed Data December 2021 Communications Of The Acm

Speculative Writing Prompt Graphic Organizer Classroom Writing Elementary Writing Third Grade Writing

2 Problems On Systems Architecture Quiz 1 Cmsc 411 Docsity

1 Lecture 7 Speculative Execution And Recovery Branch Prediction And Speculative Execution Precise Interrupt Reorder Buffer Ppt Download

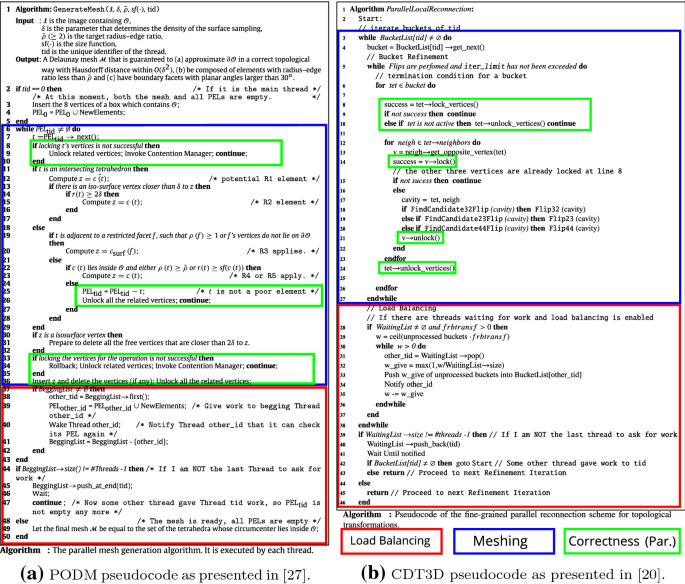

Tasking Framework For Adaptive Speculative Parallel Mesh Generation Springerlink

Dynamic Scheduling And Speculation Ppt Download

Systems And Devices 3 Sys3 Speculative Execution Tomasulo S Algorithm For Loops How To Run Studocu

Dynamic Scheduling And Speculation Ppt Download

The University Of Adelaide School Of Computer Science Ppt Download

Dynamic Scheduling With Speculation Computer Architecture

Dynamic Scheduling And Speculation Ppt Download

Speculative Taint Tracking Stt A Comprehensive Protection For Speculatively Accessed Data December 2021 Communications Of The Acm

Systems And Devices 3 Sys3 Speculative Execution Tomasulo S Algorithm For Loops How To Run Studocu

Comments

Post a Comment